题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[单选题]

4位超前进位加法器的计算延时()。

A.基本与1位全加器计算延时的4倍相同

B.基本与1位全加器计算延时相同

C.基本与1位全加器计算延时的2倍相同

D.基本与1位全加器计算延时的1/2相同

查看答案

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

A.基本与1位全加器计算延时的4倍相同

B.基本与1位全加器计算延时相同

C.基本与1位全加器计算延时的2倍相同

D.基本与1位全加器计算延时的1/2相同

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“4位超前进位加法器的计算延时()。”相关的问题

更多“4位超前进位加法器的计算延时()。”相关的问题

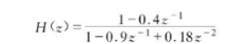

研究下面的系统函数:

(a)计算H(z)的零点和极点。

(b)若系数舍入成4位(包括符号位)的定点补码表示,计算系统函数系数量化后的零点和极点。