题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[主观题]

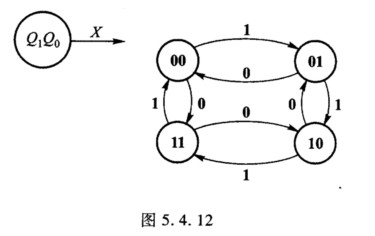

试用JK触发器设计一个模4的可逆计数器。要求控制端X=1,为递增计数;X=0时,为递减计数。状态转换图如

图5.4.12所示。试画出逻辑电路图。

查看答案

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“试用JK触发器设计一个模4的可逆计数器。要求控制端X=1,为…”相关的问题

更多“试用JK触发器设计一个模4的可逆计数器。要求控制端X=1,为…”相关的问题

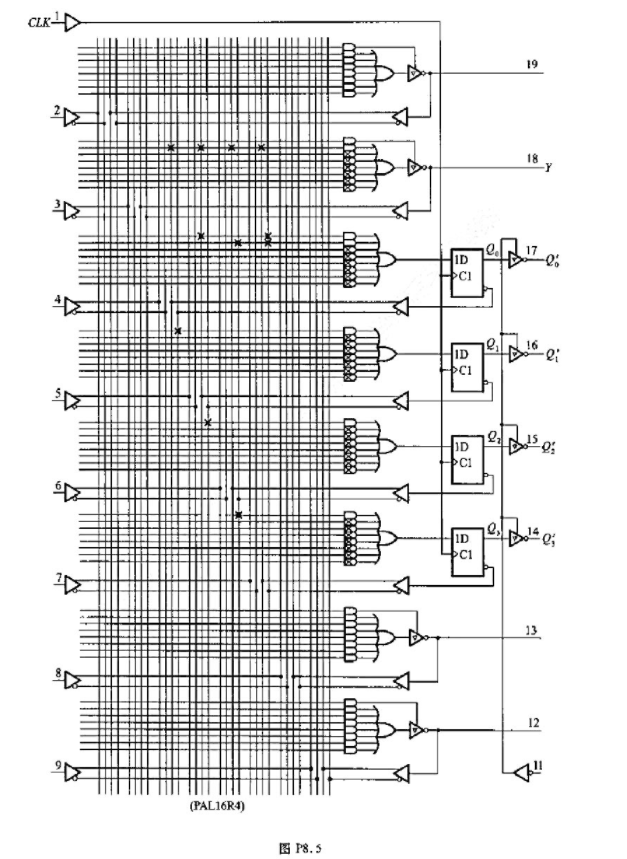

用触发器实现同步时序电路。 (1)用J-K触发器设计一个模为8的格雷码同步计数器。 (2)用D触发器设计上述题目。 (3)几点说明。