更多“设计一个波形发生器电路,要求产生图P11.10所给定的电压波…”相关的问题

更多“设计一个波形发生器电路,要求产生图P11.10所给定的电压波…”相关的问题

第1题

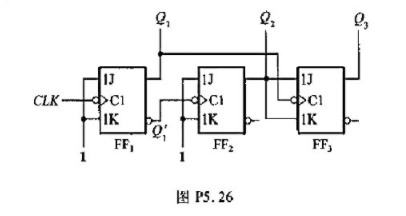

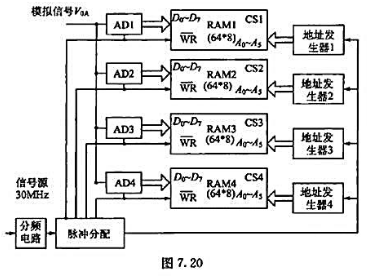

某系统为了提高采样速率,采用4片模数(全并行A/D)转换器构成并行交替式数据采集系统,原理框图如

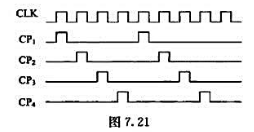

某系统为了提高采样速率,采用4片模数(全并行A/D)转换器构成并行交替式数据采集系统,原理框图如图7.20所示.系统信号源为30MHz的方波,时钟信号CLK为10MHz(要求占空比为1:1).并行交替式数据采集系统利用4片ADC轮流对同一个模拟输入信号进行采样,分别存人各路对应的64单元的存储器中,其对应各路AD所需的采样信号波形如图7.21所示,脉冲分配电路可用计数器+译码器构成.试根据系统设计参数要求,完成各部分电路的设计,器件任选.

(1)分频电路;

(2)脉冲分配电路;

(3)地址发生器电路设计;

(4)说明每个地址发生器所使用的时钟信号分别是什么?

第2题

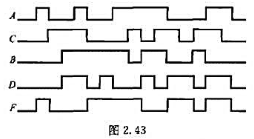

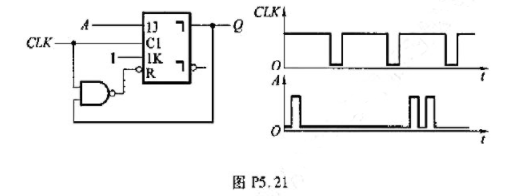

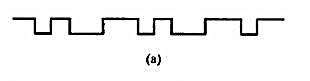

利用D触发器构成的移位寄存器配合适当的门电路,设计产生图3.26(a)所示的脉冲序列信号发生器.

利用D触发器构成的移位寄存器配合适当的门电路,设计产生图3.26(a)所示的脉冲序列信号发生器.

第4题

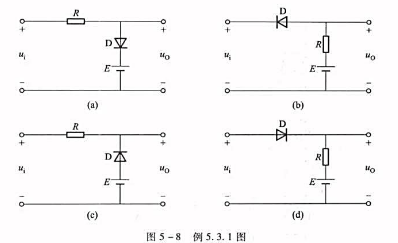

在图5-8的各电路图中,E=4V,ui=8sin(ωt)V,试分别画出输出电压u0的波形,二极管的正向压

在图5-8的各电路图中,E=4V,ui=8sin(ωt)V,试分别画出输出电压u0的波形,二极管的正向压

点击查看答案

降忽略不计。

第8题

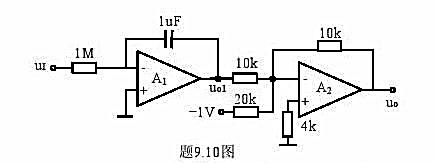

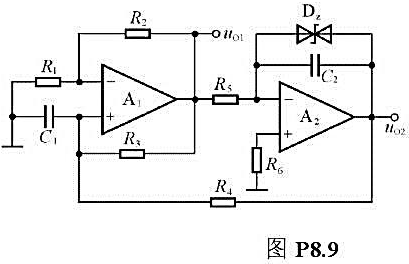

图P8.9所示电路为正交正弦波振荡电路,它可产生频率相同的正弦信号和余弦信号.已知稳压管的稳定

电压±Uz=±6V,R1=R2=R3=R4=R5=R,C1=C2=C.

点击查看答案

(1)试分析电路为什么能够满足产生正弦波振荡的条件;

(2)求出电路的振荡频率;

(3)画出uo1和uo2的波形图,要求表示出它们的相位关系,并分别求出它们的峰值.

第9题

设计一个对2F8H进行读写操作的端口译码电路,要求分别用:(1)门电路,(2)门电路和74LS138译码器。

设计一个对2F8H进行读写操作的端口译码电路,要求分别用:(1)门电路,(2)门电路和74LS138译码器。

点击查看答案

第11题

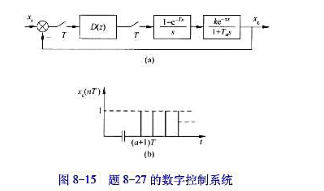

结构如图8-15(a)所示的数字控制系统。其中,τ-aT,a为正整数,T为采样周期。试设计数字控制器D(z),

结构如图8-15(a)所示的数字控制系统。其中,τ-aT,a为正整数,T为采样周期。

试设计数字控制器D(z),使系统在单位阶跃输入作用下,输出量Xt(nT)满足图8-15(b)所示的波形。

如果结果不匹配,请

如果结果不匹配,请