题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[主观题]

如果输入端CLK的频率不固定,则计数器不能作为定时器作用。()

如果输入端CLK的频率不固定,则计数器不能作为定时器作用。()

此题为判断题(对,错)。

查看答案

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

此题为判断题(对,错)。

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“如果输入端CLK的频率不固定,则计数器不能作为定时器作用。(…”相关的问题

更多“如果输入端CLK的频率不固定,则计数器不能作为定时器作用。(…”相关的问题

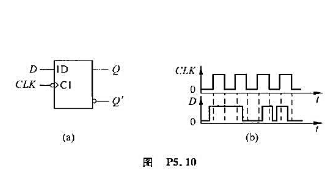

画出图P5.10(a)中边沿触发D触发器输出端Q和Q'的电压波形。时钟脉冲CLK和输入端D的电压波形如图P5.10(b)所示。设触发器的初始状态为Q=0。

4(b)所示。设触发器的初始状态为Q=0。