题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

尽管脉冲电路的种类很多,但构成电路的基本元件只是()、()、()和()等。

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

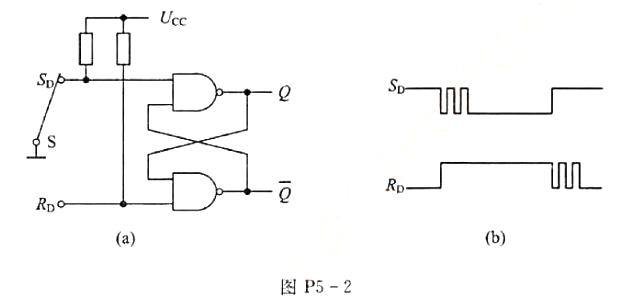

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“尽管脉冲电路的种类很多,但构成电路的基本元件只是()、()、…”相关的问题

更多“尽管脉冲电路的种类很多,但构成电路的基本元件只是()、()、…”相关的问题

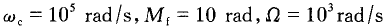

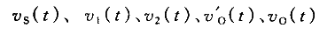

图NP5-16(a)所示脉冲计数式鉴频电路。图中,vs(t)是输入调频信号经限幅后的调频脉冲电压, ,Cd和Rd构成微分网络将vs(t)变换为双向微分脉冲序列,而后利用晶体二极管D的单向导电性,将双向脉冲变换为单向脉冲,去触发由T1和T2构成的单稳态电路,产生调频方波,最后通过低通滤波器RφCφ。取出解调电压,试画出

,Cd和Rd构成微分网络将vs(t)变换为双向微分脉冲序列,而后利用晶体二极管D的单向导电性,将双向脉冲变换为单向脉冲,去触发由T1和T2构成的单稳态电路,产生调频方波,最后通过低通滤波器RφCφ。取出解调电压,试画出 的波形,并求出解调电压vo(t)的表达式。

的波形,并求出解调电压vo(t)的表达式。

提示:单稳态电路产生的调频方波,其峰值近似为[R1/(R1+Rc)]Vcc,宽度近似为0.69RBC1。

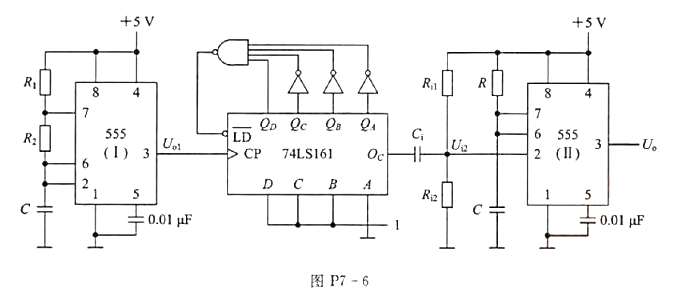

图P7-6是由两个555定时器和一片74LS161构成的脉冲电路。

(1)试说明电路各部分的功能。

(2)若555(Ⅰ)片R1=10kΩ, R2=20 kΩ, C=0.01μF,求U01端波形的周期T。

(3) 74LS161的Oc端与CP端脉冲分频比为多少?

(4)若555(Ⅱ)片的R=10 kΩ, C=0.05 μF,则U0的输出脉宽Tw为多少?

(5)画出U0、Oc和U0端的波形图。

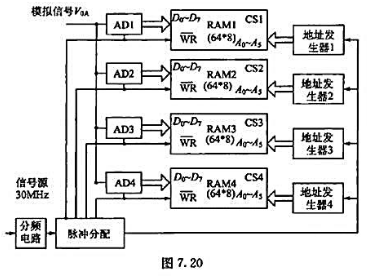

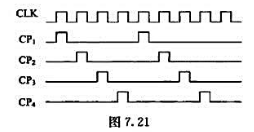

某系统为了提高采样速率,采用4片模数(全并行A/D)转换器构成并行交替式数据采集系统,原理框图如图7.20所示.系统信号源为30MHz的方波,时钟信号CLK为10MHz(要求占空比为1:1).并行交替式数据采集系统利用4片ADC轮流对同一个模拟输入信号进行采样,分别存人各路对应的64单元的存储器中,其对应各路AD所需的采样信号波形如图7.21所示,脉冲分配电路可用计数器+译码器构成.试根据系统设计参数要求,完成各部分电路的设计,器件任选.

(1)分频电路;

(2)脉冲分配电路;

(3)地址发生器电路设计;

(4)说明每个地址发生器所使用的时钟信号分别是什么?

运放构成的基本放大电路有()、()和差动输入的放大电路。它们均为运放的()应用。运放构成的比较器一般是利用了其()特性。

运放构成的基本放大电路有()、()和差动输入放大电路。它门均为运放的()应用,运放构成的比较器一般是利用了其()特性。

A.双管并联,得到双倍的输出电流和输出功率

B. 构成推挽电路,减小输出波形的失真

C. 双管并联,得到双倍的器件耐压,减少损坏几率

D. 双管并联,使每个功率管的失真互相补偿,减少失真,降低杂散发射

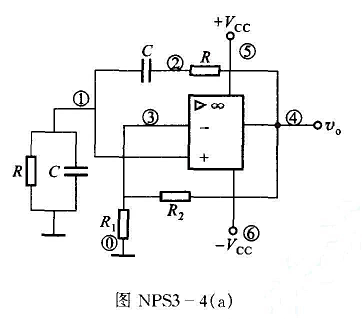

V,R=10kΩ,C=1μF,R1=5kΩ,R2=10kΩ。试分析电路,记录输出电压波形,测试振荡频率。(提示:为给振荡电路一个起始冲激信号,电源电压Vcc采用起始电压V1=5V,TD、TR、TF均为0,脉冲宽度PW=1ms,高度V2=10V的脉冲源。)