题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[主观题]

用4位加法器74LS283和4位2选1数据选择器74LS157设计一个可控码组转换器。当控制信号C=0时实现5421

码到8421码的转换;当C=1时实现2421码到842l码的转换。

查看答案

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“用4位加法器74LS283和4位2选1数据选择器74LS15…”相关的问题

更多“用4位加法器74LS283和4位2选1数据选择器74LS15…”相关的问题

A.基本与1位全加器计算延时的4倍相同

B.基本与1位全加器计算延时相同

C.基本与1位全加器计算延时的2倍相同

D.基本与1位全加器计算延时的1/2相同

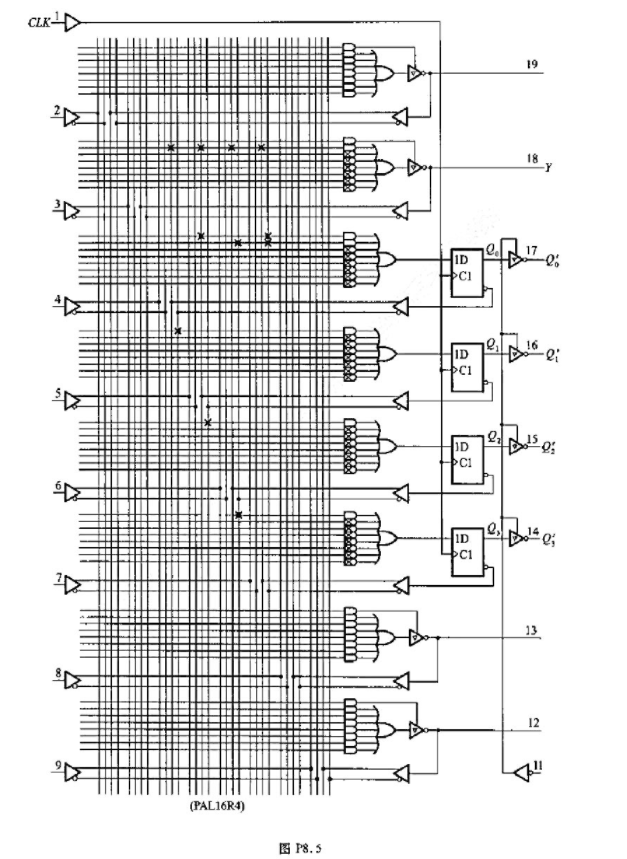

用PAL16R6设计一个4位二进制计数器,要求:

(1)具有并行置数功能。并行数据输入为P0,P1,P2,P3,控制信号为

(2)具有加/减计数功能。控制信号为

(3)具有并行输出Q0,Q1,Q2,Q3。

(4)具有进位输出C和借位输出B。

组,用与其汉明距离最近的汉明码码字所对应的4位信息符号来代表,通过无噪声信道进行传输:在接收端,用接收的4位信息符号所对应的码字表示信源分组。

(1)求编码器的码率和编码系统的平均失真。

(2)将(1) 的结果与R(D)比较(设失真测度为汉明失真)。

(3)对于任意1,应用(2-1,2 -l-1)汉明编码,求码率和平均失真。