题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

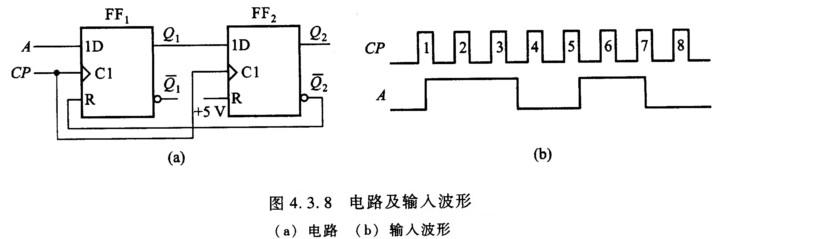

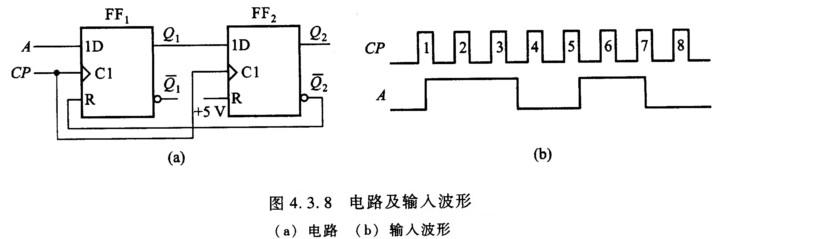

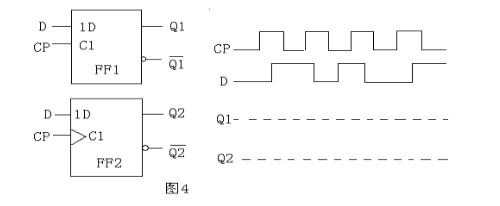

由两个D触发器组成的电路及输入波形如图4.3.8(a)、(b)所示,设Q1、Q2的初态均为0。试画出Q1、Q2的输出

由两个D触发器组成的电路及输入波形如图4.3.8(a)、(b)所示,设Q1、Q2的初态均为0。试画出Q1、Q2的输出波形。

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

由两个D触发器组成的电路及输入波形如图4.3.8(a)、(b)所示,设Q1、Q2的初态均为0。试画出Q1、Q2的输出波形。

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“由两个D触发器组成的电路及输入波形如图4.3.8(a)、(b…”相关的问题

更多“由两个D触发器组成的电路及输入波形如图4.3.8(a)、(b…”相关的问题

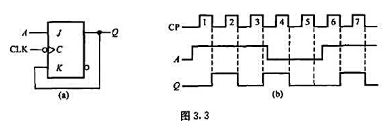

JK触发器组成图3.3(a)所示电路.试分析电路的逻辑功能.已知电路CLK和A的输入波形如图3.3(b)所示.设Q输出初态为0,画出Q的波形.

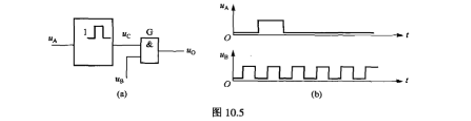

为上升沿触发式,哲稳态持续时间为400us,uB为频率10kHz的脉冲信号,根据给定条件分别画出uC及输出uO的波形.

电路及输入波形如图所示,其中FF1是维持-阻塞D触发器,FF2是边沿JK触发器,根据CP和A、B的输入波形画出Q1和Q2的输出波形。设触发器的初态均为0。

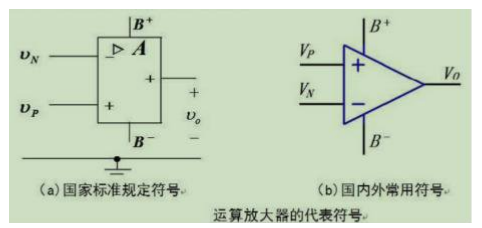

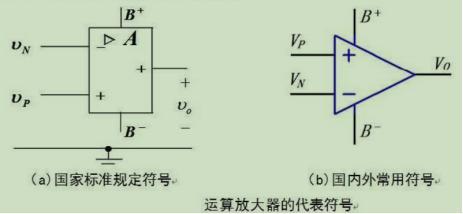

如图,关于集成电路运算放大器的说法,下列错误的是()。

A.在运算放大器的内部,输入级由差分式放大电路组成,利用它的电路对称性可提高整个电路的性能

B.中间电压放大级的主要作用是提高电压増益,它可由一级或多级放大电路组成

C.输出级能为负载提供一定的功率,电路由两个电源B+和B-供电

D.整个电路设计成两个输入端,分别为同相输入端N和和反向输入端P,—个输出端O

如图,关于集成电路运算放大器的说法,下列错误的是()。

A.在运算放大器的内部,输入级由差分式放大电路组成,利用它的电路对称性可提高整个电路的性能

B.中间电压放大级的主要作用是提高电压増益,它可由一级或多级放大电路组成

C.输出级能为负载提供一定的功率.电路由两个电源B+和B-供电

D.整个电路设计成两个输入端,分别为同相输入端N和和反向输入端P.—个输出端O

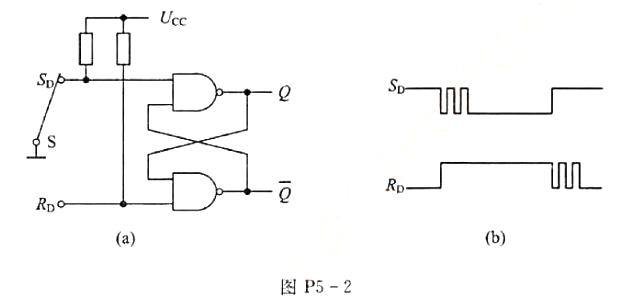

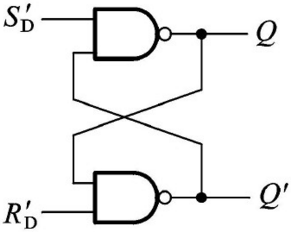

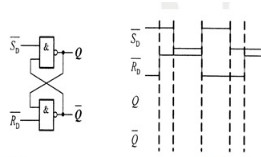

画出图5.1.1由与非门组成的SR锁存器输出端Q、Q'的电压波形,输入端S'D、R'D的电压波形如图5.1.1所示。

初始状态为0的输入为低电平有效的基本RS触发器,非R与非S端的输入信号波形如图13.3所示,求Q和非Q的波形。

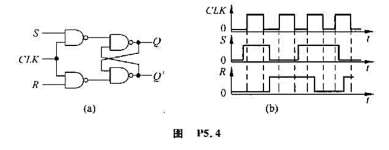

4(b)所示。设触发器的初始状态为Q=0。

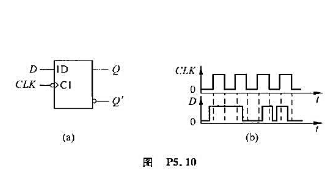

画出图P5.10(a)中边沿触发D触发器输出端Q和Q'的电压波形。时钟脉冲CLK和输入端D的电压波形如图P5.10(b)所示。设触发器的初始状态为Q=0。