题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[主观题]

用同步十进制计数器74160设计一个可变进制计数器,要求在控制信号M=0时为五进制,而在M=1时为七进制。可以附加必要的门电路。请标明计数输入端与进位输出端。

用同步十进制计数器74160设计一个可变进制计数器,要求在控制信号M=0时为五进制,而在M=1时为七进制。可以附加必要的门电路。请标明计数输入端与进位输出端。

查看答案

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“ 用同步十进制计数器74160设计一个可变进制计数器,要求在…”相关的问题

更多“ 用同步十进制计数器74160设计一个可变进制计数器,要求在…”相关的问题

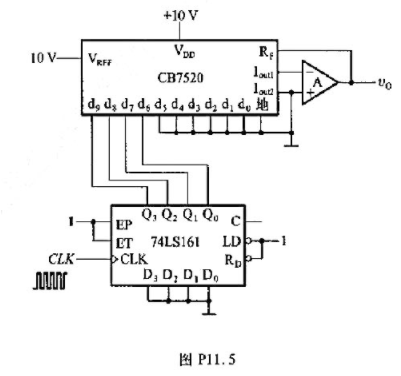

图P11.5所示电路是用CB7520和同步十六进制计数器74LS161组成的波形发生器电路.已知CB7520的 ,试画出输出电压v0的波形,并标出波形图上各点电压的幅度.

,试画出输出电压v0的波形,并标出波形图上各点电压的幅度.