题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[主观题]

触发器的两个输出端电平总是处于()状态,1个是高电平()时,另一个必定是低电平()。

触发器的两个输出端电平总是处于()状态,1个是高电平()时,另一个必定是低电平()。

查看答案

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“触发器的两个输出端电平总是处于()状态,1个是高电平()时,…”相关的问题

更多“触发器的两个输出端电平总是处于()状态,1个是高电平()时,…”相关的问题

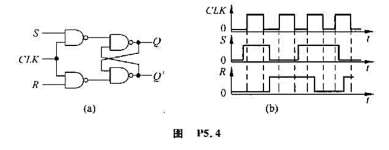

4(b)所示。设触发器的初始状态为Q=0。

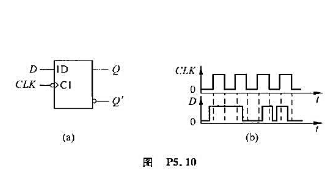

画出图P5.10(a)中边沿触发D触发器输出端Q和Q'的电压波形。时钟脉冲CLK和输入端D的电压波形如图P5.10(b)所示。设触发器的初始状态为Q=0。

A.NMOS漏极接VDD,源极加一个负载电阻,即构成一个倒相器

B.当VGS=0,NMOS倒相器处于截止状态,VDS接近VDD

C.当NMOS管导通时,输出电压VD下降

D.管子工作于截止与导通两个状态,故倒相器起了开关的作用

计算题:用示波器附带的探头将“校正输出”信号(0.3V)连接到通道1输入端。将探头衰减比置于×10,即将输入信号衰减10倍,调节“电平”旋钮使仪器触发,此时在屏幕上显示出高度为多少的信号?