更多“在低频模式下,波特率发生器使用1个预分频器和()个调制器产生…”相关的问题

更多“在低频模式下,波特率发生器使用1个预分频器和()个调制器产生…”相关的问题

第2题

低频信号发生器的频率波段钮在100~1KHz,“×1”钮在“4”,“×0.1”钮在“6”,“×0.01”钮在“5”则此时仪器输出信号的频率为()。

A.465HZ

B.465KHZ

C.46.5HZ

D.46.5KHZ

第4题

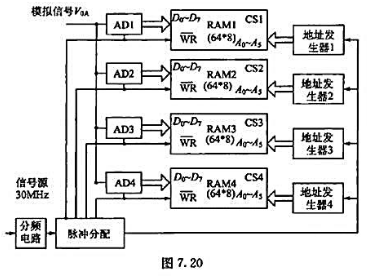

某系统为了提高采样速率,采用4片模数(全并行A/D)转换器构成并行交替式数据采集系统,原理框图如

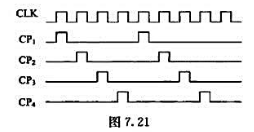

某系统为了提高采样速率,采用4片模数(全并行A/D)转换器构成并行交替式数据采集系统,原理框图如图7.20所示.系统信号源为30MHz的方波,时钟信号CLK为10MHz(要求占空比为1:1).并行交替式数据采集系统利用4片ADC轮流对同一个模拟输入信号进行采样,分别存人各路对应的64单元的存储器中,其对应各路AD所需的采样信号波形如图7.21所示,脉冲分配电路可用计数器+译码器构成.试根据系统设计参数要求,完成各部分电路的设计,器件任选.

(1)分频电路;

(2)脉冲分配电路;

(3)地址发生器电路设计;

(4)说明每个地址发生器所使用的时钟信号分别是什么?

第11题

XD-22A型低频信号发生器的主振级采用RC振荡器电路,由热敏电阻Rt组成的负反馈支路的作用是稳幅,该热敏电阻的类型是()。

XD-22A型低频信号发生器的主振级采用RC振荡器电路,由热敏电阻Rt组成的负反馈支路的作用是稳幅,该热敏电阻的类型是()。

点击查看答案

如果结果不匹配,请

如果结果不匹配,请