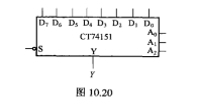

更多“电路如图,所用器件为4选1数据选择器。 写出四选一数据选择器…”相关的问题

更多“电路如图,所用器件为4选1数据选择器。 写出四选一数据选择器…”相关的问题

第2题

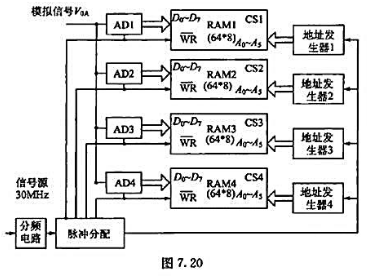

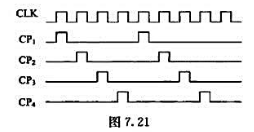

某系统为了提高采样速率,采用4片模数(全并行A/D)转换器构成并行交替式数据采集系统,原理框图如

某系统为了提高采样速率,采用4片模数(全并行A/D)转换器构成并行交替式数据采集系统,原理框图如图7.20所示.系统信号源为30MHz的方波,时钟信号CLK为10MHz(要求占空比为1:1).并行交替式数据采集系统利用4片ADC轮流对同一个模拟输入信号进行采样,分别存人各路对应的64单元的存储器中,其对应各路AD所需的采样信号波形如图7.21所示,脉冲分配电路可用计数器+译码器构成.试根据系统设计参数要求,完成各部分电路的设计,器件任选.

(1)分频电路;

(2)脉冲分配电路;

(3)地址发生器电路设计;

(4)说明每个地址发生器所使用的时钟信号分别是什么?

第3题

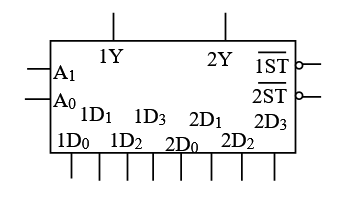

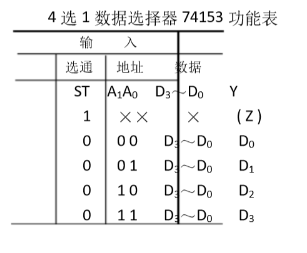

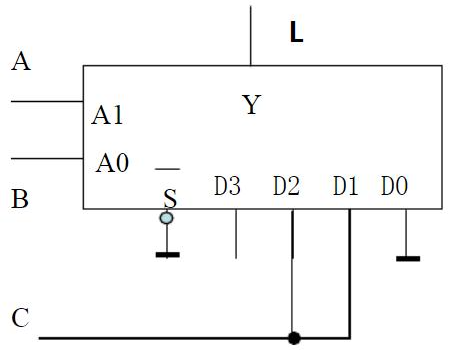

试用双4选1数据选择器74153设计一个全减器,它能完成二进制减法运算S=(A—B—C),CO为借位输出,写

试用双4选1数据选择器74153设计一个全减器,它能完成二进制减法运算S=(A—B—C),CO为借位输出,写

点击查看答案

出设计过程,画出逻辑电路。4选1数据选择器功能表和符号图分别见功能表和附图。

第7题

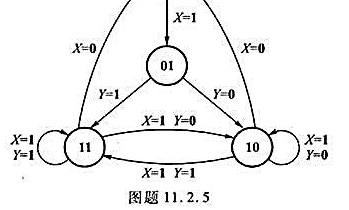

一个数字系统控制单元的状态图如图题11.2.5所示,试画出等效的ASM图(状态框是空的),并用D触发器

一个数字系统控制单元的状态图如图题11.2.5所示,试画出等效的ASM图(状态框是空的),并用D触发器和数据选择器实现控制单元电路。

第9题

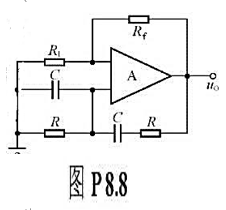

电路如图P8.8所示.(1)为使电路产生正弦波振荡,标出集成运放的“+”和“-”,并说明电路是哪种正弦波

电路如图P8.8所示.

(1)为使电路产生正弦波振荡,标出集成运放的“+”和“-”,并说明电路是哪种正弦波振荡电路.

(2)若R1短路,则电路将产生什么现象?

(3)若R1断路,则电路将产生什么现象?

(4)若Rf短路,则电路将产生什么现象

(5)若Rf断路,则电路将产生什么现象?

第10题

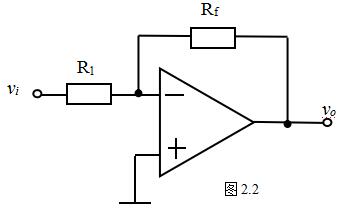

放大电路如图2.2所示,(1)试说明电路引入的反馈类型;(2)如果Rf=10K,试确定电阻R1,使得放大电路

放大电路如图2.2所示,(1)试说明电路引入的反馈类型;(2)如果Rf=10K,试确定电阻R1,使得放大电路

点击查看答案

增益为-10。(3)确定电路的输入电阻;(4)如果给电阻R1串联一个电容C,电路能否放大直流信号?给出下限频率的表达式。

写出四选一数据选择器的输出逻辑表达式。

写出四选一数据选择器的输出逻辑表达式。

如果结果不匹配,请

如果结果不匹配,请