更多“机车信号记录器的信号波形采集的ADC为()。”相关的问题

更多“机车信号记录器的信号波形采集的ADC为()。”相关的问题

第1题

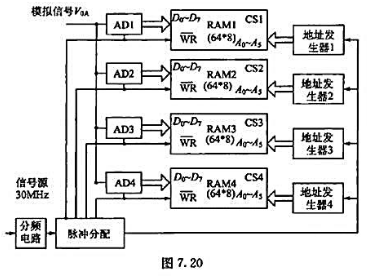

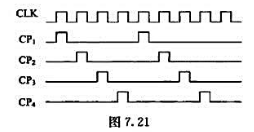

某系统为了提高采样速率,采用4片模数(全并行A/D)转换器构成并行交替式数据采集系统,原理框图如

某系统为了提高采样速率,采用4片模数(全并行A/D)转换器构成并行交替式数据采集系统,原理框图如图7.20所示.系统信号源为30MHz的方波,时钟信号CLK为10MHz(要求占空比为1:1).并行交替式数据采集系统利用4片ADC轮流对同一个模拟输入信号进行采样,分别存人各路对应的64单元的存储器中,其对应各路AD所需的采样信号波形如图7.21所示,脉冲分配电路可用计数器+译码器构成.试根据系统设计参数要求,完成各部分电路的设计,器件任选.

(1)分频电路;

(2)脉冲分配电路;

(3)地址发生器电路设计;

(4)说明每个地址发生器所使用的时钟信号分别是什么?

第3题

JT1-CZ2000型主体化机车信号车载系统由哪些部件构成的()

JT1-CZ2000型主体化机车信号车载系统由哪些部件构成的()

点击查看答案

A.主体化机车信号主机(含机车信号记录器)

B.机车信号带电源接线盒

C.机车信号双路接收线圈

D.机车信号显示器

第7题

一体化机车信号主机记录板对机车信号运行过程中的有关动态信息进行采集,可通过()转存基本状态数据。

一体化机车信号主机记录板对机车信号运行过程中的有关动态信息进行采集,可通过()转存基本状态数据。

点击查看答案

第10题

以课程介绍的ATF20B型函数信号发生器为例,通过按下选项按钮可选中波形的某个参数,以下属于选项按钮的选项是()。

A.频率按钮

B.波形按钮

C.偏移(偏置)按钮

D.Channel(通道)按钮

如果结果不匹配,请

如果结果不匹配,请