更多“异步方式下,8251A的时钟CLK比数据传输率大()倍”相关的问题

更多“异步方式下,8251A的时钟CLK比数据传输率大()倍”相关的问题

第4题

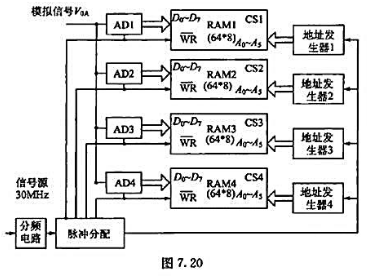

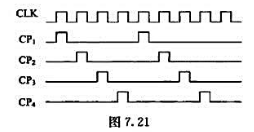

某系统为了提高采样速率,采用4片模数(全并行A/D)转换器构成并行交替式数据采集系统,原理框图如

某系统为了提高采样速率,采用4片模数(全并行A/D)转换器构成并行交替式数据采集系统,原理框图如图7.20所示.系统信号源为30MHz的方波,时钟信号CLK为10MHz(要求占空比为1:1).并行交替式数据采集系统利用4片ADC轮流对同一个模拟输入信号进行采样,分别存人各路对应的64单元的存储器中,其对应各路AD所需的采样信号波形如图7.21所示,脉冲分配电路可用计数器+译码器构成.试根据系统设计参数要求,完成各部分电路的设计,器件任选.

(1)分频电路;

(2)脉冲分配电路;

(3)地址发生器电路设计;

(4)说明每个地址发生器所使用的时钟信号分别是什么?

第5题

串行异步通信的实现,必须作到()。

A.通信双方有同步时钟的传送,以实现同步

B.一块数据传送结束时,用循环冗余校验码进行校验

C.以字符为传送信息的单位,按约定配上起始位、停止位和校验位

D.块与块间用同步字符01111110隔开

第6题

关于数据库级容灾,以下说法错误的是()

A.数据库级的容灾技术,是针对于固定的数据库设计的容灾方案

B.数据库级容灾支持广域网,但需要单独的硬件支持

C.数据库级容灾主要是通过传输数据日志,并在灾备站点进行重放(Replay)来实现的

D.数据库级容灾,在异步方式下会丢失较多数据,至少丢失一个日志文件

第11题

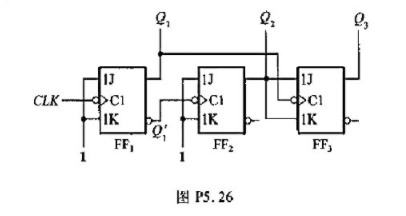

n位异步二进制加法计数器由n个()组成,最低位触发器的时钟端与()相连;如果触发器的时钟是下降

n位异步二进制加法计数器由n个()组成,最低位触发器的时钟端与()相连;如果触发器的时钟是下降

点击查看答案

沿有效,则高位触发器的时钟端与相邻低位触发器的()相连;如果是上升沿有效,则与()相连。

如果结果不匹配,请

如果结果不匹配,请